| <i></i> |                      |

|---------|----------------------|

| Oki,    | Network Solutions    |

|         | for a Global Society |

|         |                      |

**PEDL9041A-02** Issue Date: Mar. 15, 2002

# OKI Semiconductor ML9041A-xxA/xxB

**Preliminary**

# DOT MATRIX LCD CONTROLLER DRIVER

# **GENERAL DESCRIPTION**

The ML9041A used in combination with an 8-bit or 4-bit microcontroller controls the operation of a character type dot matrix LCD.

# FEATURES

- Easy interfacing with 8-bit or 4-bit microcontroller

- Switchable between serial and parallel interfaces

- Dot-matrix LCD controller/driver for a small (5  $\times$  7 dots) or large (5  $\times$  10 dots) font

- Built-in circuit allowing automatic resetting at power-on

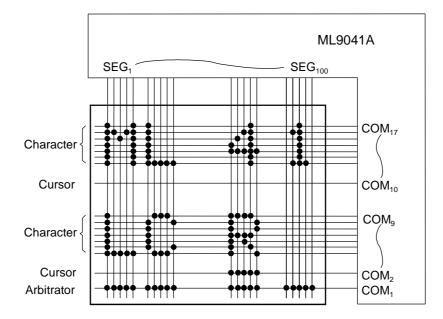

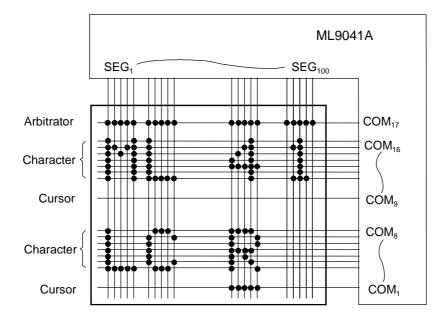

- Built-in 17 common signal drivers and 100 segment signal drivers

- Built-in character generation ROM capable of generating 160 small characters (5 × 7 dots) or 32 large characters (5 × 10 dots)

- Creation of character patterns by programming: up to 8 small character patterns (5 × 8 dots) or up to 4 large character patterns (5 × 11 dots)

- Built-in RC oscillation circuit using external or internal resistors

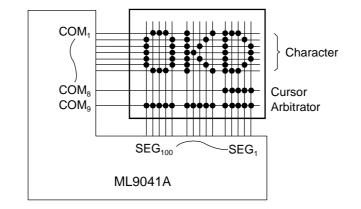

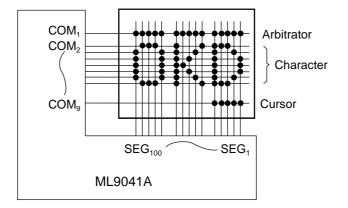

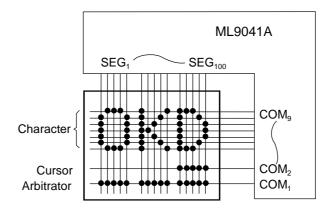

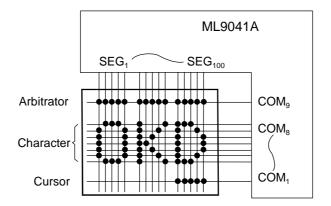

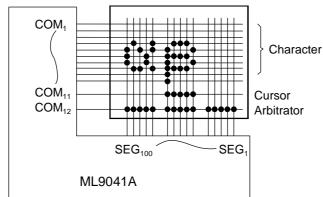

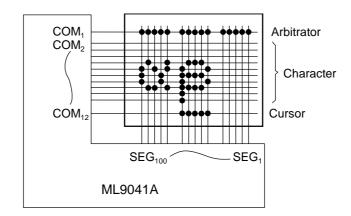

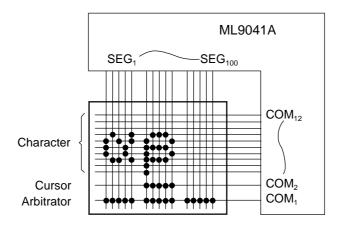

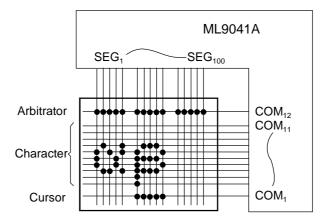

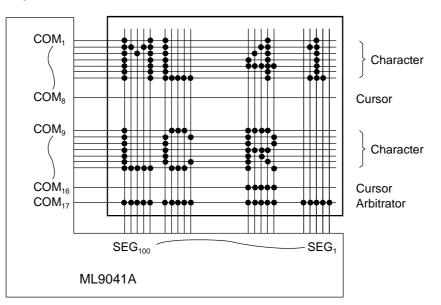

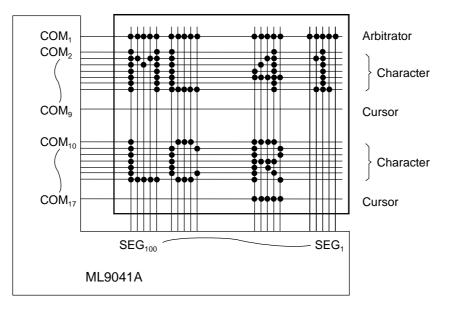

- Program-selectable duties: 1/9 duty (1 line: 5 × 7 dots + cursor + arbitrator), 1/12 duty (1 line: 5 × 10 dots + cursor + arbitrator), or 1/17 duty (2 lines: 5 × 7 dots + cursor + arbitrator)

- Built-in bias dividing resistors to drive the LCD

- Bi-directional transfer of segment outputs

- Bi-directional transfer of common outputs

- 100-dot arbitrator display

- Line display shifting

- Built-in contrast control circuit

- Built-in voltage multiplier circuit

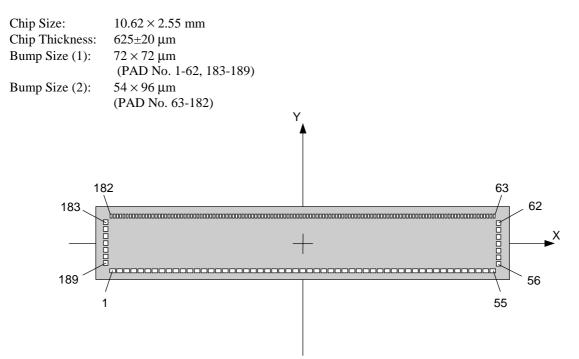

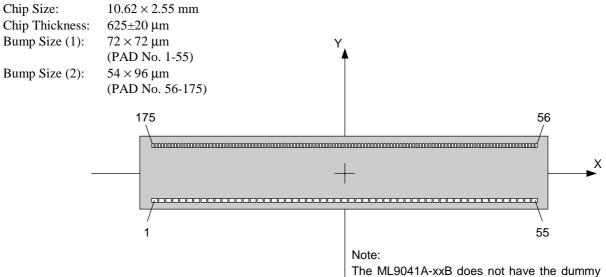

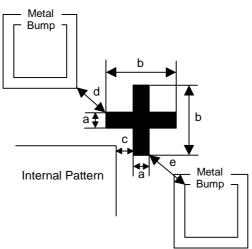

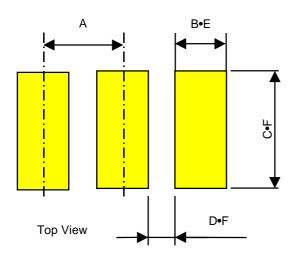

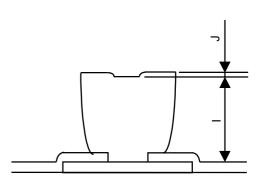

- Gold Bump Chip

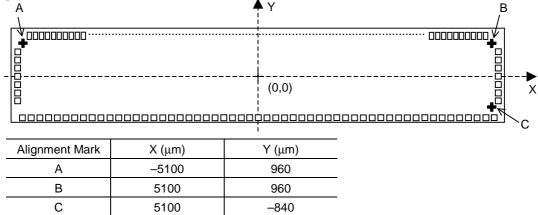

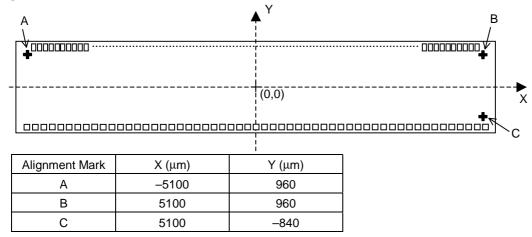

- With dummy bumps on both sides of the chip: ML9041A-xxA CVWA

- Without dummy bumps on both sides of the chip: ML9041A-xxB CVWA \*xx indicates a character generator ROM code number.

- \*01A and 01B indicate general character generator ROM code numbers.

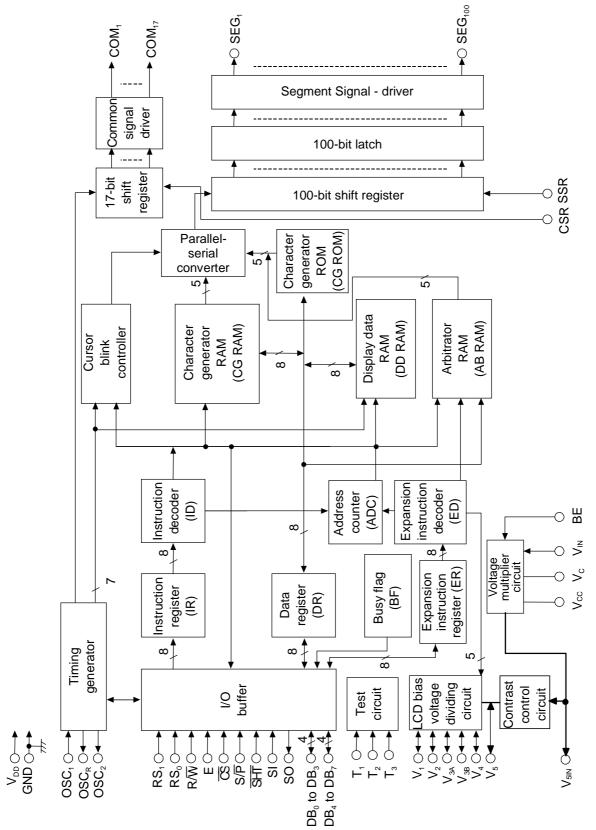

#### **BLOCK DIAGRAM**

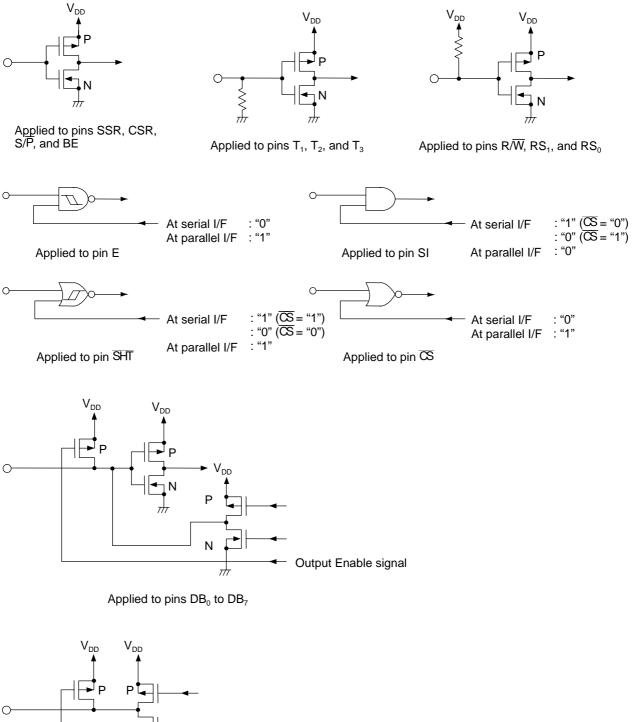

#### **I/O CIRCUITS**

# PIN DESCRIPTIONS

| Symbol                                 | Description                                                                                                                                                                                                                                                                           |                       |                                                      |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------|--|--|--|

| R/W                                    | The input pin with a pull-up resistor to select Read ("H") or Write ("L") in the Parallel I/F Mode.                                                                                                                                                                                   |                       |                                                      |  |  |  |

|                                        | This pin should be                                                                                                                                                                                                                                                                    | open in the Serial    | I/F Mode.                                            |  |  |  |

|                                        | The input pins with                                                                                                                                                                                                                                                                   | a pull-up resistor    | to select a register in the Parallel I/F Mode.       |  |  |  |

|                                        | RS₁                                                                                                                                                                                                                                                                                   | $RS_0$                | Name of register                                     |  |  |  |

| $RS_0, RS_1$                           | Н                                                                                                                                                                                                                                                                                     | Н                     | Data register                                        |  |  |  |

| $RO_0, RO_1$                           | Н                                                                                                                                                                                                                                                                                     | L                     | Instruction register                                 |  |  |  |

|                                        | L                                                                                                                                                                                                                                                                                     | L                     | Expansion Instruction register                       |  |  |  |

|                                        | This pin should be                                                                                                                                                                                                                                                                    | open in the Serial    | I/F Mode.                                            |  |  |  |

| E                                      | The input pin for da activating instruction                                                                                                                                                                                                                                           |                       | tween the CPU and the ML9041A and for<br>I/F Mode.   |  |  |  |

|                                        | This pin should be                                                                                                                                                                                                                                                                    | open in the Serial    | I/F Mode.                                            |  |  |  |

| DB <sub>0</sub> to DB <sub>3</sub>     | The input/output pins to transfer data of lower-order 4 bits between the CPU and the ML9041A in the Parallel I/F Mode. The pins are not used for the 4-bit interface and serial interface.<br>Each pin is equipped with a pull-up resistor, so this pin should be open when not used. |                       |                                                      |  |  |  |

| $DB_4$ to $DB_7$                       | The input/output pins to transfer data of upper 4 bits between the CPU and the ML9041A in the Parallel I/F Mode. The pins are not used for the serial interface.<br>Each pin is equipped with a pull-up resistor, so this pin should be open in the Serial I/F Mode when not used.    |                       |                                                      |  |  |  |

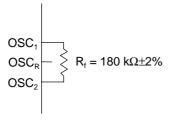

|                                        | The clock oscillatio<br>ML9041A by instru                                                                                                                                                                                                                                             |                       | r LCD drive signals and the operation of the ne CPU. |  |  |  |

| OSC <sub>1</sub><br>OSC <sub>2</sub>   | To input external c should be open.                                                                                                                                                                                                                                                   | lock, the $OSC_1$ pin | should be used. The $OSC_R$ and the $OSC_2$ pine     |  |  |  |

| OSC <sub>2</sub><br>OSC <sub>R</sub>   | To start oscillation with an external resistor, the resistor should be connected between the $OSC_1$ and $OSC_2$ pins. The $OSC_R$ pin should be open.                                                                                                                                |                       |                                                      |  |  |  |

|                                        | To start oscillation with an internal resistor, the $OSC_2$ and $OSC_R$ pins should be short-circuited outside the ML9041A. The $OSC_1$ pin should be open.                                                                                                                           |                       |                                                      |  |  |  |

|                                        | The LCD common                                                                                                                                                                                                                                                                        | signal output pins    |                                                      |  |  |  |

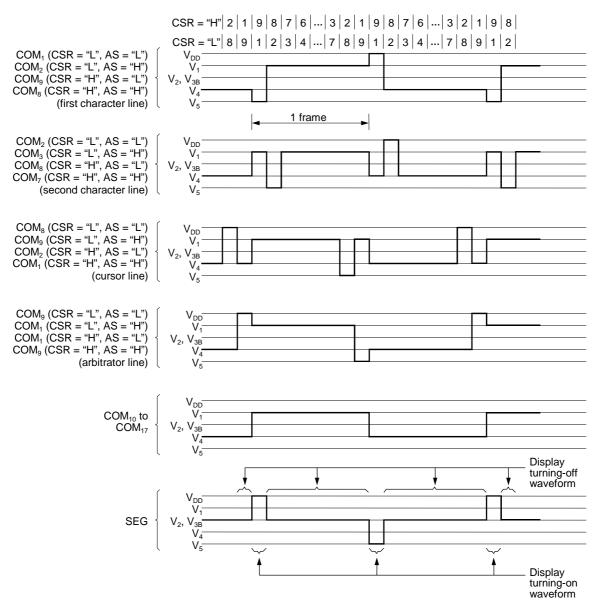

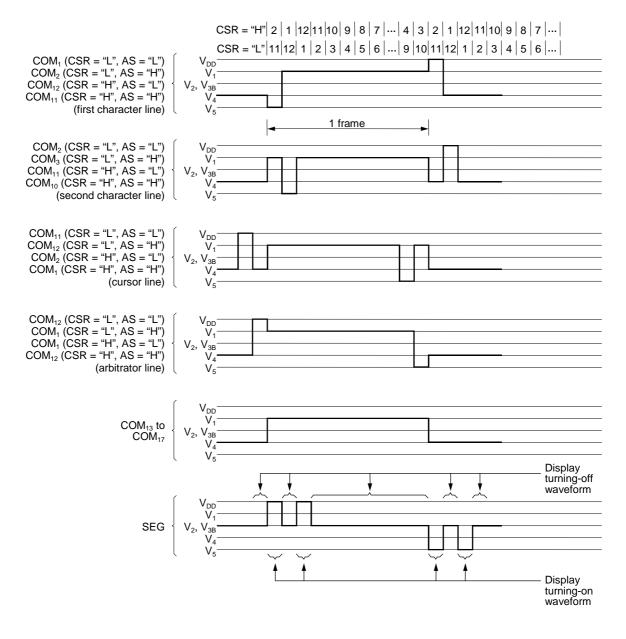

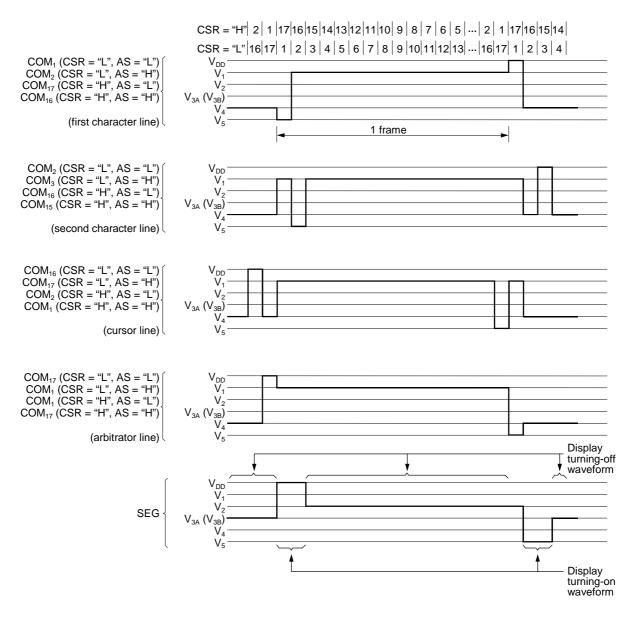

| $COM_1$ to $COM_{17}$                  | For 1/9 duty, non-selectable voltage waveforms are output via $COM_{10}$ to $COM_{17}$ . For 1/12 duty, non-selectable voltage waveforms are output via $COM_{13}$ to $COM_{17}$ .                                                                                                    |                       |                                                      |  |  |  |

| SEG <sub>1</sub> to SEG <sub>100</sub> | The LCD segment                                                                                                                                                                                                                                                                       | signal output pins    |                                                      |  |  |  |

| Symbol                          | Description                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | The input pin to select the transfer direction of the common signal output data.                                                                                                                                                                                                                                                                  |

| CSR                             | At 1/n duty, data is transferred from COM1 to COMn when "L" is applied to this pin and transferred from COMn to COM1 when "H" is applied to this pin.                                                                                                                                                                                             |

|                                 | The input pin to select the transfer direction of the segment signal output data.                                                                                                                                                                                                                                                                 |

| SSR                             | "L": Data transfer from SEG <sub>1</sub> to SEG <sub>100</sub>                                                                                                                                                                                                                                                                                    |

|                                 | "H": Data transfer from SEG <sub>100</sub> to SEG <sub>1</sub>                                                                                                                                                                                                                                                                                    |

|                                 | The pins to output bias voltages to the LCD.                                                                                                                                                                                                                                                                                                      |

| $V_1$ , $V_2,V_{3A},V_{3B},V_4$ | For 1/4 bias : The $V_2$ and $V_{3B}$ pins are shorted.                                                                                                                                                                                                                                                                                           |

|                                 | For 1/5 bias : The $V_{3A}$ and $V_{3B}$ pins are shorted.                                                                                                                                                                                                                                                                                        |

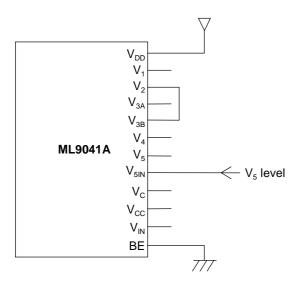

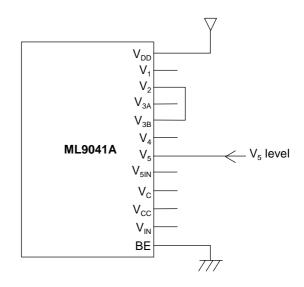

|                                 | The input pin to enable or disable the voltage multiplier circuit.                                                                                                                                                                                                                                                                                |

|                                 | "L" disables the voltage multiplier circuit. "H" enables the voltage multiplier circuit.                                                                                                                                                                                                                                                          |

| BE                              | The voltage multiplier circuit doubles the input voltage between $V_{DD}$ and $V_{IN}$ and the multiplied voltage referenced to $V_{DD}$ is output to the $V_{5IN}$ pin. The voltage multiplier circuit can be used only when generating a level lower than GND.                                                                                  |

| V <sub>IN</sub>                 | The pin to input voltage to the voltage multiplier.                                                                                                                                                                                                                                                                                               |

|                                 | The pins to supply the LCD drive voltage.                                                                                                                                                                                                                                                                                                         |

|                                 | The LCD drive voltage is supplied to the V <sub>5</sub> pin when the voltage multiplier is not used (BE = "0") and the internal contrast adjusting circuit is also not used. At this time, the $V_{5IN}$ pin should be open.                                                                                                                      |

| $V_5$ , $V_{5IN}$               | The LCD drive voltage is supplied to the $V_{5IN}$ pin when the voltage multiplier is not used (BE = "0") but the internal contrast adjusting circuit is used. At this time, the V <sub>5</sub> pin should be open.                                                                                                                               |

|                                 | When the voltage multiplier is used (BE = "1"), the V <sub>5</sub> pin should be open (the multiplied voltage is output to the V <sub>5IN</sub> pin). In this case, the internal contrast adjusting circuit must be used. Capacitors for the voltage multiplier should be connected between the V <sub>DD</sub> pin and the V <sub>5IN</sub> pin. |

| V <sub>c</sub>                  | The pin to connect the positive pin of the capacitor for the voltage multiplier. Leave the pin open when the voltage multiplier circuit is not used.                                                                                                                                                                                              |

| V <sub>cc</sub>                 | The pin to connect the negative pin of the capacitor used for the voltage multiplier.<br>Leave the pin open when the voltage multiplier circuit is not used.                                                                                                                                                                                      |

#### PEDL9041A-02

#### ML9041A-xxA/xxB

| Symbol                                           | Description                                                                                                                                  |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>1</sub> , T <sub>2</sub> , T <sub>3</sub> | The input pins for test circuits (normally open). Each of these pins is equipped with a pull-down resistor, so this pin should be left open. |

| V <sub>DD</sub>                                  | The power supply pin.                                                                                                                        |

| GND                                              | The ground level input pin.                                                                                                                  |

|                                                  | The input pin to select the serial or parallel interface.                                                                                    |

| S/P                                              | "L" selects the parallel interface.                                                                                                          |

|                                                  | "H" selects the serial interface.                                                                                                            |

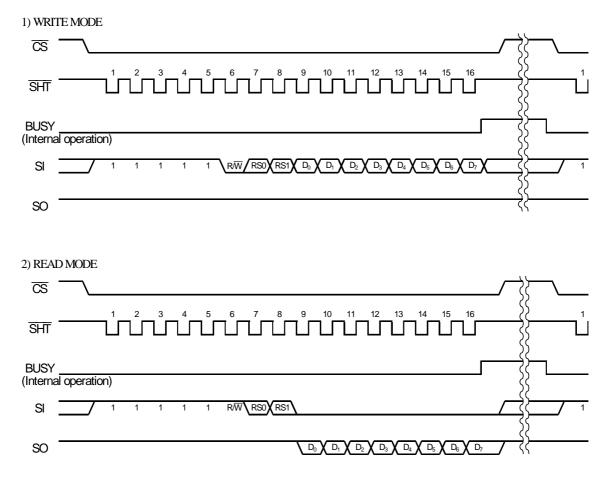

|                                                  | The pin to enable this IC in the serial I/F mode.                                                                                            |

| CS                                               | "L" enables this IC.                                                                                                                         |

| 65                                               | "H" disables this IC.                                                                                                                        |

|                                                  | This pin should be open in the parallel I/F mode.                                                                                            |

|                                                  | The pin to input shift clock in the serial I/F mode.                                                                                         |

|                                                  | Data inputting to the SI pin is carried out synchronizing with the rising edge of this clock signal.                                         |

| SHT                                              | Data outputting from the SO pin is carried out synchronizing with the falling edge of this clock signal.                                     |

|                                                  | This pin should be open in the parallel I/F mode.                                                                                            |

|                                                  | The pin to input DATA in the serial I/F mode.                                                                                                |

| SI                                               | Data inputting to this pin is carried out synchronizing with the rising edge of the SHT signal.                                              |

|                                                  | This pin should be open in the parallel I/F mode.                                                                                            |

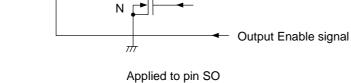

|                                                  | The pin to output DATA in the serial I/F mode.                                                                                               |

| SO                                               | Data inputting to this pin is carried out synchronizing with the falling edge of the SHT signal.                                             |

|                                                  | This pin should be open in the parallel I/F mode.                                                                                            |

|                                                  | NC pin.                                                                                                                                      |

| DUMMY                                            | Leave this pin open.                                                                                                                         |

# ABSOLUTE MAXIMUM RATINGS

|                     |                                                                                       |           |                                |      | (GND = 0 V)                                                                                                                                                                                                                       |

|---------------------|---------------------------------------------------------------------------------------|-----------|--------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter           | Symbol                                                                                | Condition | Rating                         | Unit | Applicable pins                                                                                                                                                                                                                   |

| Supply Voltage      | V <sub>DD</sub>                                                                       | Ta = 25°C | -0.3 to +6.5                   | V    | V <sub>DD</sub> –GND                                                                                                                                                                                                              |

| LCD Driving Voltage | V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> ,<br>V <sub>4</sub> , V <sub>5</sub> | Ta = 25°C | $V_{DD}$ –7.5 to $V_{DD}$ +0.3 | V    | $V_1, V_4, V_5, V_{5IN}, V_2, V_{3A}, V_{3B}$                                                                                                                                                                                     |

| Input Voltage       | Vı                                                                                    | Ta = 25°C | –0.3 to $V_{DD}$ +0.3          | V    | $R/\overline{W}$ , E, $\overline{SHT}$ , CSR, $S/\overline{P}$ ,<br>SSR, SI, RS <sub>0</sub> , RS <sub>1</sub> , BE, $\overline{CS}$ ,<br>T <sub>1</sub> to T <sub>3</sub> , DB <sub>0</sub> to DB <sub>7</sub> , V <sub>IN</sub> |

| Storage Temperature | T <sub>STG</sub>                                                                      | —         | -55 to +150                    | °C   | —                                                                                                                                                                                                                                 |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                              | Symbol                                        | Condition | Range      | Unit | Applicable pins                  |

|----------------------------------------|-----------------------------------------------|-----------|------------|------|----------------------------------|

| Supply Voltage                         | V <sub>DD</sub>                               |           | 2.7 to 5.5 | V    | V <sub>DD</sub> –GND             |

| LCD Driving Voltage                    | V <sub>DD</sub> -V <sub>5</sub><br>(See Note) | _         | 3.3 to 7.0 | V    | $V_{DD} - V_5$<br>( $V_{5IN}$ )  |

| Voltage Multipler<br>Operating Voltage | V <sub>MUL</sub>                              | BE = "1"  | 2.7 to 3.5 | V    | V <sub>DD</sub> -V <sub>IN</sub> |

| Operating Temperature                  | T <sub>op</sub>                               | _         | -40 to +85 | °C   | —                                |

- Note: This voltage should be applied across  $V_{DD}$  and  $V_5$ . The following voltages are output to the  $V_1$ ,  $V_2$ ,  $V_{3A}$  ( $V_{3B}$ ) and  $V_4$  pins:

- 1/4 bias  $V_1 = \{V_{DD} - (V_{DD} - V_5)/4\} \pm 0.15 V$   $V_2 = V_{3B} = \{V_{DD} - (V_{DD} - V_5)/2\} \pm 0.15 V$   $V_4 = \{V_{DD} - 3 \times (V_{DD} - V_5)/4\} \pm 0.15 V$

- 1/5 bias

$\begin{array}{l} V_1 = \{V_{DD} - (V_{DD} - V_5)/5\} \pm 0.15 \ V \\ V_2 = \{V_{DD} - 2 \times (V_{DD} - V_5)/5\} \pm 0.15 \ V \\ V_{3A} = V_{3B} = \{V_{DD} - 3 \times (V_{DD} - V_5)/5\} \pm 0.15 \ V \\ V_4 = \{V_{DD} - 4 \times (V_{DD} - V_5)/5\} \pm 0.15 \ V \end{array}$

The voltages at the V11, V2, V3A (V3B), V4 and V5 pins should satisfy

$\begin{array}{l} \mathsf{V}_{\text{DD}} > \mathsf{V}_1 > \mathsf{V}_2 > \mathsf{V}_{3\text{A}} \; (\mathsf{V}_{3\text{B}}) > \mathsf{V}_4 > \mathsf{V}_5. \\ (\text{Higher} \leftarrow \qquad \rightarrow \text{Lower}) \end{array}$

- \* If the chip is attached on a substrate using COG technology, the chip tends to be susceptible to electrical characteristics of the chip due to trace resistance on the glass substrate. It is recommended to use the chip by confirming that it operates on the glass substrate properly. Trace resistance, especially, V<sub>DD</sub> and V<sub>SS</sub> trace resistance, between the chip on the LCD panel and the flexible cable should be designed as low as possible. Trace resistance that cannot be very well decreased, larger size of the LCD panel, or greater trace capacitance between the microcontroller and the ML9041A device can cause device malfunction. In order to avoid the device malfunction, power noise should be reduced by serial interfacing of the microcontroller and the ML9041A device.

- \* Do not apply short-circuiting across output pins and across an output pin and an input/output pin or the power supply pin in the output mode.

ML9041A-xxA/xxB

(GND = 0 V)

# **ELECTRICAL CHARACTERISTICS**

## **DC Characteristics**

| DC Characteristics                               |                   |                                                                                               | (0                                                                                                                 | GND = 0 V            | , V <sub>DD</sub> = | 2.7 to 5.5          | 5 V, Ta | a = −40 to +85°C)                                                              |  |

|--------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|---------------------|---------|--------------------------------------------------------------------------------|--|

| Parameter                                        | Symbol            | Cond                                                                                          | ition                                                                                                              | Min.                 | Тур.                | Max.                | Unit    | Applicable pin                                                                 |  |

| "H" Input Voltage                                | V <sub>IH</sub>   |                                                                                               |                                                                                                                    | $0.8V_{DD}$          | _                   | V <sub>DD</sub>     | V       | $R/\overline{W}$ , $RS_0$ , $RS_1$ ,<br>E, $DB_0$ to $DB_7$ ,<br>SHT, S/P, SI, |  |

| "L" Input Voltage                                | V <sub>IL</sub>   |                                                                                               |                                                                                                                    | 0                    | _                   | $0.2V_{DD}$         | v       | $\overline{CS}$ , $OSC_1$ , $SSR$ , $CSR$ , $BE$                               |  |

| "H" Output Voltage 1                             | V <sub>OH1</sub>  | I <sub>OH</sub> = -0.1 mA                                                                     |                                                                                                                    | $0.75V_{DD}$         | —                   | —                   | V       | $DB_0$ to $DB_7$ , SO                                                          |  |

| "L" Output Voltage 1                             | V <sub>OL1</sub>  | I <sub>OL</sub> = +0.1 mA                                                                     |                                                                                                                    | _                    |                     | $0.2V_{DD}$         |         | 0 17                                                                           |  |

| "H" Output Voltage 2                             | V <sub>OH2</sub>  | I <sub>OH</sub> = −13 μA                                                                      |                                                                                                                    | $0.9V_{DD}$          | —                   | —                   | V       | OSC <sub>2</sub>                                                               |  |

| "L" Output Voltage 2                             | V <sub>OL2</sub>  | I <sub>OL</sub> = +13 μA                                                                      | 1                                                                                                                  | _                    | —                   | $0.1V_{\text{DD}}$  | •       |                                                                                |  |

|                                                  | V <sub>CH</sub>   | $I_{OCH} = -4 \ \mu A$                                                                        |                                                                                                                    | V <sub>DD</sub> -0.3 | —                   | V <sub>DD</sub>     |         |                                                                                |  |

| COM Voltage Drop                                 | V <sub>CMH</sub>  | $I_{OCMH} = \pm 4 \ \mu A$                                                                    | $V_{DD} - V_5 = 5 V$                                                                                               | V <sub>1</sub> –0.3  | —                   | V <sub>1</sub> +0.3 | V       | COM <sub>1</sub> to                                                            |  |

| Com Voltage Brop                                 | V <sub>CML</sub>  | $I_{OCML} = \pm 4 \ \mu A$                                                                    | Note 1                                                                                                             | V <sub>4</sub> -0.3  | —                   | V <sub>4</sub> +0.3 | v       | COM <sub>17</sub>                                                              |  |

|                                                  | V <sub>CL</sub>   | $I_{OCL} = +4 \ \mu A$                                                                        |                                                                                                                    | V <sub>5</sub>       | —                   | V <sub>5</sub> +0.3 |         |                                                                                |  |

|                                                  | V <sub>SH</sub>   | $I_{OSH} = -4 \ \mu A$                                                                        |                                                                                                                    | V <sub>DD</sub> -0.3 | —                   | V <sub>DD</sub>     |         |                                                                                |  |

| SEG Voltage Drop                                 | V <sub>SMH</sub>  | $I_{OSMH} = \pm 4 \ \mu A$                                                                    | $V_{DD} - V_5 = 5 V$                                                                                               | V <sub>2</sub> -0.3  | —                   | V <sub>2</sub> +0.3 | V       | SEG₁ to                                                                        |  |

| SEG Vollage Drop                                 | V <sub>SML</sub>  | $I_{OSML} = \pm 4 \ \mu A$                                                                    | Note 1                                                                                                             | V <sub>3</sub> –0.3  | —                   | V <sub>3</sub> +0.3 | v       | SEG <sub>100</sub>                                                             |  |

|                                                  | V <sub>SL</sub>   | l <sub>osL</sub> = +4 μA                                                                      |                                                                                                                    | V <sub>5</sub>       | -                   | V <sub>5</sub> +0.3 |         |                                                                                |  |

| Input Leakage Current                            | IIL               | $V_{DD} = 5 \text{ V}, \text{ V}_{I} = 5 \text{ V} \text{ or } 0 \text{ V}$                   |                                                                                                                    | _                    | _                   | 1.0                 | μA      | E, SSR, CSR,<br>BE, SHT, S/P,<br>CS, SI                                        |  |

|                                                  |                   | $V_{DD} = 5 V, V_{I} = 0$                                                                     | GND                                                                                                                | 10                   | 25                  | 61                  |         |                                                                                |  |

| Input Current 1                                  | 1                 | Excluding curre through the pull                                                              | $V_{DD} = 5 V, V_1 = V_{DD},$<br>Excluding current flowing through the pull-up resistor and the output driving MOS |                      | _                   | 2.0                 | μΑ      | $R/\overline{W}$ , $RS_0$ , $RS_1$ , $DB_0$ to $DB_7$ , $SO$                   |  |

|                                                  |                   | $V_{DD} = 5 V, V_{I} = 7$                                                                     |                                                                                                                    | 15                   | 45                  | 105                 |         |                                                                                |  |

| Input Current 2                                  | 112               | $V_{DD} = 5 V, V_1 = 0$<br>Excluding curre<br>through the pull                                | GND<br>ent flowing                                                                                                 | _                    |                     | 2.0                 | μΑ      | T <sub>1</sub> , T <sub>2</sub> , T <sub>3</sub>                               |  |

| Supply Current                                   | I <sub>DD</sub>   | $V_{DD} = 5 V$                                                                                | Note 2                                                                                                             |                      | _                   | 1.2                 | mA      | V <sub>DD</sub> –GND                                                           |  |

| LCD Bias Resistor                                | $R_{LB}$          |                                                                                               |                                                                                                                    | 2.5                  | 4.0                 | 6.0                 | kΩ      | $V_{DD}, V_1, V_2, V_{3A}, V_{3B}, V_4, V_5$                                   |  |

| Oscillation Frequency<br>of External Resistor Rf | f <sub>osc1</sub> | Rf = 180 kΩ±2%                                                                                | % Note 3                                                                                                           | 175                  | 270                 | 400                 | kHz     | OSC <sub>1</sub> , OSC <sub>2</sub>                                            |  |

| Oscillation Frequency<br>of Internal Resistor Rf | f <sub>osc2</sub> | OSC <sub>1</sub> : Open Note 4<br>OSC <sub>2</sub> and OSC <sub>R</sub> : Short-<br>circuited |                                                                                                                    | 140                  | 270                 | 480                 | kHz     | OSC <sub>1</sub> , OSC <sub>2</sub> ,<br>OSC <sub>R</sub>                      |  |

| Clock Input<br>Frequency                         | f <sub>in</sub>   | OSC <sub>2</sub> , OSC <sub>R</sub> : C<br>Input from OSC                                     | -                                                                                                                  | 125                  | —                   | 480                 | kHz     |                                                                                |  |

| C Input Clock Duty                               | f <sub>duty</sub> |                                                                                               | Note 5                                                                                                             | 45                   | 50                  | 55                  | %       | OSC1                                                                           |  |

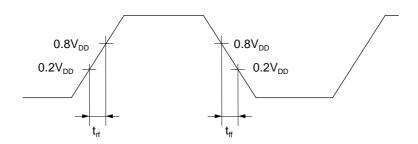

| Input Clock Rise                                 | f <sub>rf</sub>   |                                                                                               | Note 6                                                                                                             | _                    | _                   | 0.2                 | μs      |                                                                                |  |

| Input Clock Fall Time                            | f <sub>ff</sub>   |                                                                                               | Note 6                                                                                                             | —                    | —                   | 0.2                 | μs      |                                                                                |  |

#### **OKI** Semiconductor

| Parameter                           | Symbol                               | Condition                                                                                    |           | Min. | Тур. | Max.                         | Unit | Applicable<br>pins              |

|-------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------|-----------|------|------|------------------------------|------|---------------------------------|

| Voltage Multiplier<br>Input Voltage | V <sub>MUL</sub>                     | Note 7                                                                                       | Note 7    |      | _    | 3.5                          | V    | $V_{DD} - V_{IN}$               |

| Voltage Multiplier                  |                                      | $V_{DD} = 2.7 \text{ V}, V_{IN} = 0 \text{ V}$<br>f = 125 kHz<br>A capacitor for the voltage | 1/5 bias  | 4.1  | _    | $(V_{DD} - V_{IN}) \times 2$ |      |                                 |

| Output Voltage                      | V <sub>50UT</sub>                    | multiplier = 1 to 4.7 μF<br>No load<br>BE = "H"                                              | 1/4 bias  | 3.9  | _    | $(V_{DD} - V_{IN}) \times 2$ | V    | $V_{DD} - V_{5IN}$              |

|                                     |                                      | $V_{DD} = 5 V$ , $V_{5IN} = -2 V$ ,<br>Contrast data: 1F, No load                            | 1/5 bias, | 6.6  |      | _                            |      |                                 |

|                                     | V <sub>LCD</sub><br>MAX              | $V_{DD} = 5 \text{ V}, V_{5IN} = -2 \text{ V},$<br>Contrast data: 1F, No load                | 1/4 bias, | 6.6  | _    |                              | v    |                                 |

| Maximum and                         |                                      | $V_{DD} = 4.1$ V, $V_{5IN} = 0$ V,<br>Contrast data: 1F, No load                             | 1/5 bias, | 3.8  | —    | _                            | v    |                                 |

| minimum LCD<br>drive voltages       |                                      | $V_{DD}$ = 3.9 V, $V_{SIN}$ = 0 V,<br>Contrast data: 1F, No load                             | 1/4 bias, | 3.6  | —    |                              |      |                                 |

| when internal variable resistors    |                                      | $V_{DD} = 5 \text{ V}, V_{5IN} = -2 \text{ V},$<br>Contrast data: 00, No load                | 1/5 bias, | 4.0  | —    | 4.6                          |      | V <sub>DD</sub> -V <sub>5</sub> |

| are used. Note 8                    | V <sub>LCD</sub>                     | $V_{DD} = 5 V$ , $V_{5IN} = -2 V$ ,<br>Contrast data: 00, No load                            | 1/4 bias, | 3.6  | —    | 4.2                          | v    |                                 |

|                                     | $MIN  V_{DD} = 4.1  V,  V_{5IN} = 0$ | $V_{DD} = 4.1$ V, $V_{5IN} = 0$ V,<br>Contrast data: 00, No load                             | 1/5 bias, | 2.2  | —    | 2.8                          | v    |                                 |

|                                     |                                      | $V_{DD} = 3.9$ V, $V_{5IN} = 0$ V,<br>Contrast data: 00, No load                             | 1/4 bias, | 1.9  |      | 2.5                          |      |                                 |

| Bias Voltage for                    | $V_{LCD1}$                           |                                                                                              | 1/5 bias  | 3.3  | _    | 7.0                          | v    | V                               |

| Driving LCD                         | $V_{LCD2}$                           | $V_{DD} - V_5$ Note 9                                                                        | 1/4 bias  | 3.3  | —    | 7.0                          | v    | $V_5$                           |

$(GND = 0 V, V_{DD} = 2.7 \text{ to } 5.5 V, Ta = -40 \text{ to } +85^{\circ}C)$

Note 1: Applied to the voltage drop occurring between any of the  $V_{DD}$ ,  $V_1$ ,  $V_4$  and  $V_5$  pins and any of the common pins (COM<sub>1</sub> to COM<sub>17</sub>) when the current of 4  $\mu$ A flows in or flows out at one common pin.

Also applied to the voltage drop occurring between any of the  $V_{DD}$ ,  $V_2$ ,  $V_{3A}$  ( $V_{3B}$ ) and  $V_5$  pins and any of the segment pins (SEG<sub>1</sub> to SEG<sub>100</sub>) when the current of 4  $\mu$ A flows in or flows out at one common pin.

The current of 4  $\mu A$  flows out when the output level is  $V_{\text{DD}}$  or flows in when the output level is  $V_{5}.$

Note 2: Applied to the current flowing into the  $V_{DD}$  pin when the external clock ( $f_{OSC2} = f_{in} = 270$  kHz) is fed to the internal  $R_f$  oscillation or OSC<sub>1</sub> under the following conditions:

$V_{DD} = 5 V$   $GND = V_5 = 0 V$ ,  $V_1$ ,  $V_2$ ,  $V_{3A}$  ( $V_{3B}$ ) and  $V_4$ : Open E, SSR, CSR, and BE: "L" (fixed) Other input pins: "L" or "H" (fixed) Other output pins: No load

Note 3:

The wire between OSC<sub>1</sub> and  $R_f$  and the wire between OSC<sub>2</sub> and  $R_f$  should be as short as possible. Keep OSC<sub>R</sub> open.

Note 4:

The wire between  $OSC_2$  and  $OSC_R$  should be as short as possible. Keep  $OSC_1$  open.

Note 5:

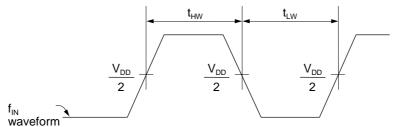

Applied to the pulses entering from the OSC<sub>1</sub> pin  $f_{duty} = t_{HW}/(t_{HW} + t_{LW}) \times 100$  (%)

Note 6:

Applied to the pulses entering from the OSC<sub>1</sub> pin

- Note 7: The maximum value of the voltage multiplier input voltage should be set at 3.5 V, and the minimum value of the voltage multiplier input voltage should be set so that the voltage multiplier output voltage meets the specification for the bias voltage for driving LCD after contrast adjustment.

- Note 8: If using the built-in contrast control circuit, control the circuit so that the voltage of  $V_{DD}$ - $V_5$  is the minimum value of the bias voltage for driving LCD or higher.

- Note 9: For 1/4 bias,  $V_2$  and  $V_{3B}$  pins are short-circuited.  $V_{3A}$  pin is open. For 1/5 bias,  $V_{3A}$  and  $V_{3B}$  pins are short-circuited.  $V_2$  pin is open.

### Switching Characteristics (The following ratings are subject to change after ES evaluation.)

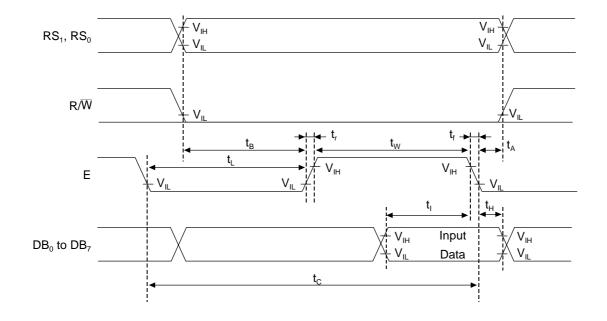

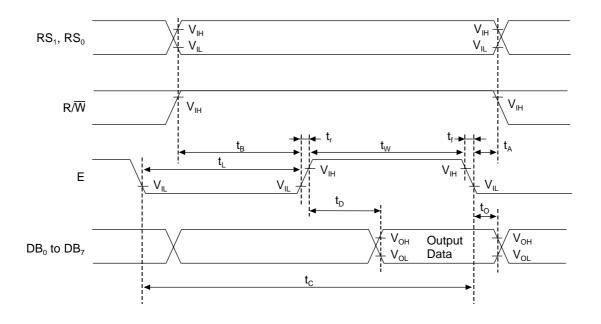

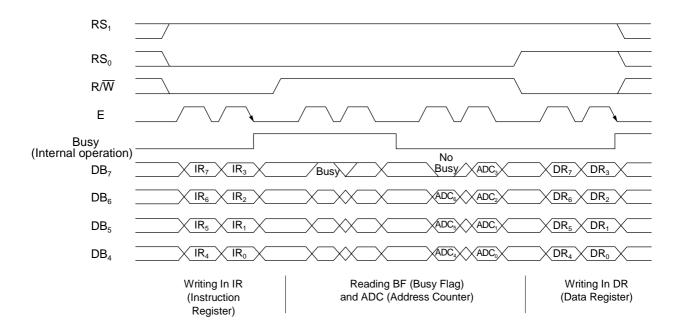

• Parallel Interface Mode

The timing for the input from the CPU (see 1) and the timing for the output to the CPU (see 2) are as shown below:

|                                                          | ,              | ()   | $-27$ to $\beta$ | 55V Ta       | 40 to +85°C) |

|----------------------------------------------------------|----------------|------|------------------|--------------|--------------|

|                                                          |                | ( •  | DD = 2.7 10      | .5 v, ta = − | +0.0+0.0 (0) |

| Parameter                                                | Symbol         | Min. | Тур.             | Max.         | Unit         |

| $R/\overline{W}$ , $RS_0$ , $RS_1$ Setup Time            | t <sub>B</sub> | 40   | —                | —            | ns           |

| E Pulse Width                                            | t <sub>w</sub> | 450  | —                | _            | ns           |

| $R/\overline{W}$ , $RS_0$ , $RS_1$ Hold Time             | t <sub>A</sub> | 10   | —                | _            | ns           |

| E Rise Time                                              | t <sub>r</sub> | —    | —                | 25           | ns           |

| E Fall Time                                              | t <sub>f</sub> | —    | —                | 25           | ns           |

| E Pulse Width                                            | tL             | 430  | _                | _            | ns           |

| E Cycle Time                                             | t <sub>c</sub> | 1000 | —                | —            | ns           |

| $DB_0$ to $DB_7$ Input Data Hold Time                    | t              | 195  | _                | _            | ns           |

| DB <sub>0</sub> to DB <sub>7</sub> Input Data Setup Time | t <sub>H</sub> | 10   | _                | _            | ns           |

1) WRITE MODE (Timing for input from the CPU)

#### **OKI** Semiconductor

#### ML9041A-xxA/xxB

#### $(V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$ Parameter Min. Max. Unit Symbol Тур. R/W, RS<sub>1</sub>, RS<sub>0</sub> Setup Time 40 — ns t<sub>B</sub> E Pulse Width 450 \_\_\_\_\_ \_\_\_\_ $\mathbf{t}_{\mathrm{W}}$ ns R/W, RS<sub>1</sub>, RS<sub>0</sub> Hold Time 10 \_\_\_ \_ ns t<sub>A</sub> E Rise Time — 25 ns t<sub>r</sub> — E Fall Time \_\_\_\_ $\mathbf{t}_{\mathrm{f}}$ \_\_\_\_ 25 ns E Pulse Width 430 \_\_\_\_ ns tL \_ E Cycle Time 1000 t<sub>C</sub> \_ ns DB<sub>0</sub> to DB<sub>7</sub> Output Data Delay Time $\mathbf{t}_{\mathsf{D}}$ \_ \_\_\_\_ 350 ns DB<sub>0</sub> to DB<sub>7</sub> Output Data Hold Time to 20 \_\_\_\_ \_ ns

#### 2) READ MODE (Timing for output to the CPU)

Note: A load capacitance of each of  $DB_0$  to  $DB_7$  must be 50 pF or less.

#### PEDL9041A-02

#### **OKI** Semiconductor

#### ML9041A-xxA/xxB

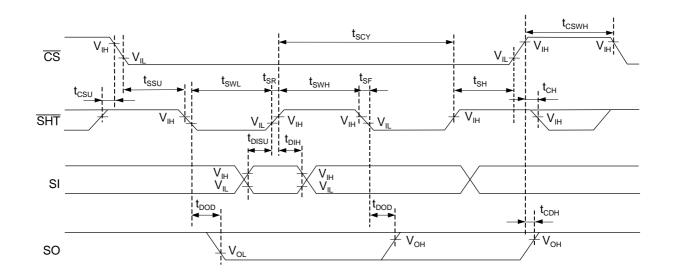

# • Serial Interface Mode

|                        |                   | ()   | $V_{\rm DD} = 2.7 \text{ to } 3$ | 5.5 V, Ta = - | 40 to +85°C) |

|------------------------|-------------------|------|----------------------------------|---------------|--------------|

| Parameter              | Symbol            | Min. | Тур.                             | Max.          | Unit         |

| SHT Cycle Time         | t <sub>SCY</sub>  | 500  | —                                | _             | ns           |

| CS Setup Time          | t <sub>csu</sub>  | 100  | —                                | —             | ns           |

| CS Hold Time           | t <sub>CH</sub>   | 100  | —                                | _             | ns           |

| CS "H" Pulse Width     | t <sub>cswh</sub> | 200  | —                                | _             | ns           |

| SHT Setup Time         | t <sub>ssu</sub>  | 60   | _                                | _             | ns           |

| SHT Hold Time          | t <sub>SH</sub>   | 200  | _                                | _             | ns           |

| SHT "H" Pulse Width    | t <sub>swH</sub>  | 200  | —                                | —             | ns           |

| SHT "L" Pulse Width    | t <sub>SWL</sub>  | 200  | —                                | _             | ns           |

| SHT Rise Time          | t <sub>sR</sub>   | _    | _                                | 50            | ns           |

| SHT Fall Time          | t <sub>SF</sub>   | —    | —                                | 50            | ns           |

| SI Setup Time          | t <sub>DISU</sub> | 100  | _                                | _             | ns           |

| SI Hold Time           | t <sub>DIH</sub>  | 100  | _                                | _             | ns           |

| Data Output Delay Time | t <sub>DOD</sub>  | _    | _                                | 160           | ns           |

| Data Output Hold Time  | t <sub>CDH</sub>  | 0    | _                                | _             | ns           |

#### FUNCTIONAL DESCRIPTION

#### Instruction Register (IR), Data Register (DR), and Expansion Instruction Register (ER)

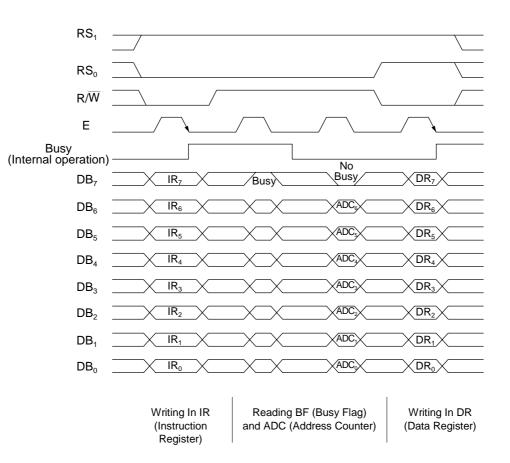

These registers are selected by setting the level of the Register Selection input pins  $RS_0$  and  $RS_1$ . The DR is selected when both  $RS_0$  and  $RS_1$  are "H". The IR is selected when  $RS_0$  is "L" and  $RS_1$  is "H". The ER is selected when both  $RS_0$  and  $RS_1$  are "L". (When  $RS_0$  is "H" and  $RS_1$  is "L", the ML9041A is not selected.)

The IR stores an instruction code and sets the address code of the display data RAM (DDRAM) or the character generator RAM (CGRAM).

The microcontroller (CPU) can write to the IR but cannot read from the IR.

The ER stores a contrast adjusting code and sets the address code of the arbitrator RAM (ABRAM).

The CPU can write to or read from the ER.

The DR stores data to be written in the DDRAM, ABRAM and CGRAM and also stores data read from the DDRAM, ABRAM and CGRAM.

The data written in the DR by the CPU is automatically written in the DDRAM, ABRAM or CGRAM.

When an address code is written in the IR or ER, the data of the specified address is automatically transferred from the DDRAM, ABRAM or CGRAM to the DR. The data of the DDRAM, ABRAM and CGRAM can be checked by allowing the CPU to read the data stored in the DR.

After the CPU writes data in the DR, the data of the next address in the DDRAM, ABRAM or CGRAM is selected to be ready for the next writing by the CPU. Similarly, after the CPU reads the data in the DR, the data of the next address in the DDRAM, ABRAM or CGRAM is set in the DR to be ready for the next reading by the CPU.

Writing in or reading from these 3 registers is controlled by changing the status of the  $R/\overline{W}$  (Read/Write) pin.

| R/W | $RS_0$ | RS₁ | Operation                                                                                                                                    |

|-----|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| L   | L      | Н   | Writing in the IR                                                                                                                            |

| н   | L      | н   | Reading the Busy flag (BF) and the address counter (ADC)                                                                                     |

| L   | Н      | Н   | Writing in the DR                                                                                                                            |

| Н   | Н      | Н   | Reading from the DR                                                                                                                          |

| L   | L      | L   | Writing in the ER                                                                                                                            |

| Н   | L      | L   | Reading the contrast code                                                                                                                    |

| L   | Н      | L   | Disabled (Not in a busy state, not performing the writes)                                                                                    |

| н   | Н      | L   | Disabled (Not in a busy state, not performing the reads.<br>Note data read by the CPU is undefined since the data bus<br>is high impedance.) |

#### Table 1 R/W pin status and register operation

#### Busy Flag (BF)

The status "1" of the Busy Flag (BF) indicates that the ML9041A is carrying out internal operation. When the BF is "1", any new instruction is ignored.

When  $R/\overline{W} = "H"$ ,  $RS_0 = "L"$  and  $RS_1 = "H"$ , the data in the BF is output to the DB<sub>7</sub>.

New instructions should be input when the BF is "0".

When the BF is "1", the output code of the address counter (ADC) is undefined.

#### **Address Counter (ADC)**

The address counter provides a read/write address for the DDRAM, ABRAM or CGRAM and also provides a cursor display address.

When an instruction code specifying DDRAM, ABRAM or CGRAM address setting is input to the pre-defined register, the register selects the specified DDRAM, ABRAM or CGRAM and transfers the address code to the ADC. The address data in the ADC is automatically incremented (or decremented) by 1 after the display data is written in or read from the DDRAM, ABRAM or CGRAM.

The data in the ADC is output to  $DB_0$  to  $DB_6$  when  $R/\overline{W} = "H"$ ,  $RS_0 = "L"$ ,  $RS_1 = "H"$  and BF = "0".

#### **Timing Generator**

The timing generator generates timing signals for the internal operation of the ML9041A activated by the instruction sent from the CPU or for the operation of the internal circuits of the ML9041A such as DDRAM, ABRAM, CGRAM and CGROM. Timing signals are generated so that the internal operation carried out for LCD displaying will not be interfered by the internal operation initiated by accessing from the CPU. For example, when the CPU writes data in the DDRAM, the display of the LCD not corresponding to the written data is not affected.

#### **Display Data RAM (DDRAM)**

This RAM stores the 8-bit character codes (see Table 2).

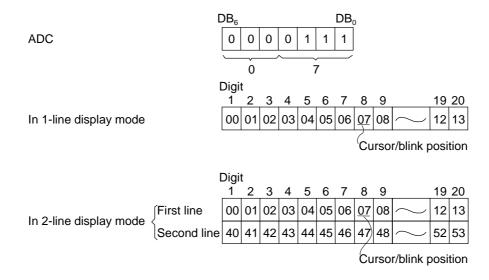

The DDRAM addresses correspond to the display positions (digits) of the LCD as shown below. The DDRAM addresses (to be set in the ADC) are represented in hexadecimal.

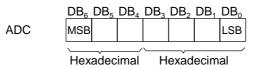

|     | $DB_6 DB_5 DB_4 DB_4$ | $DB_3 DB_2 DB_1 DB_0$ |

|-----|-----------------------|-----------------------|

| ADC | MSB                   | LSB                   |

|     | Hexadecimal           | Hexadecimal           |

(Example) Representation of DDRAM address = 12

| ADC | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

|     |   | ì |   |   | Ž | • |   |

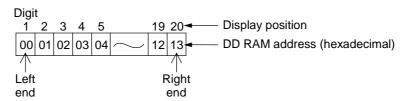

1) Relationship between DDRAM addresses and display positions (1-line display mode)

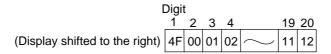

In the 1-line display mode, the ML9041A can display up to 20 characters from digit 1 to digit 20. While the DDRAM has addresses "00" to "4F" for up to 80 character codes, the area not used for display can be used as a RAM area for general data. When the display is shifted by instruction, the relationship between the LCD display and the DDRAM address changes as shown below:

|                               | Digi | t  |    |    |    |           |    |    |   |

|-------------------------------|------|----|----|----|----|-----------|----|----|---|

|                               | 1    | 2  | 3  | 4  | 5  |           | 19 | 20 |   |

| (Display shifted to the left) | 01   | 02 | 03 | 04 | 05 | $\langle$ | 13 | 14 | 1 |

**OKI** Semiconductor

- ML9041A-xxA/xxB

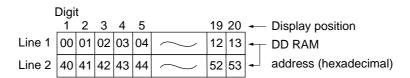

- Relationship between DDRAM addresses and display positions (2-line display mode) In the 2-line mode, the ML9041A can display up to 40 characters (20 characters per line) from digit 1 to digit 20.

Note: The DDRAM address at digit 20 in the first line is not consecutive to the DDRAM address at digit 1 in the second line.

When the display is shifted by instruction, the relationship between the LCD display and the DDRAM address changes as shown below:

|                                |        | Digi     | t  |    |    |    |               |    |    |

|--------------------------------|--------|----------|----|----|----|----|---------------|----|----|

|                                |        | <u>1</u> | 2  | 3  | 4  | 5  |               | 19 | 20 |

| (Display shifted to the right) | Line 1 | 27       | 00 | 01 | 02 | 03 | $\langle$     | 11 | 12 |

|                                | Line 2 | 67       | 40 | 41 | 42 | 43 | $\langle$     | 51 | 52 |

|                                | 1      | Digi     | t  |    |    |    |               |    |    |

|                                |        | 1        |    | 3  | 4  | 5  |               | 19 | 20 |

| (Display shifted to the left)  | Line 1 | 01       | 02 | 03 | 04 | 05 | $\Big\rangle$ | 13 | 14 |

| (Display shinted to the left)  | Line 2 | 41       | 42 | 43 | 44 | 45 | $\sim$        | 53 | 54 |

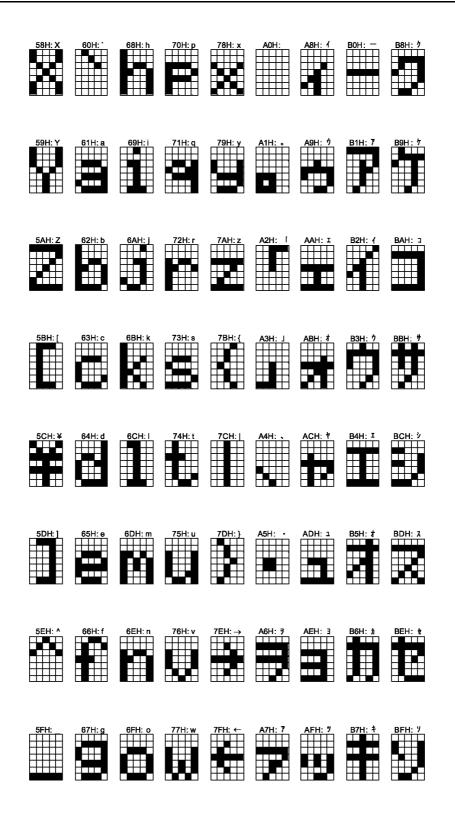

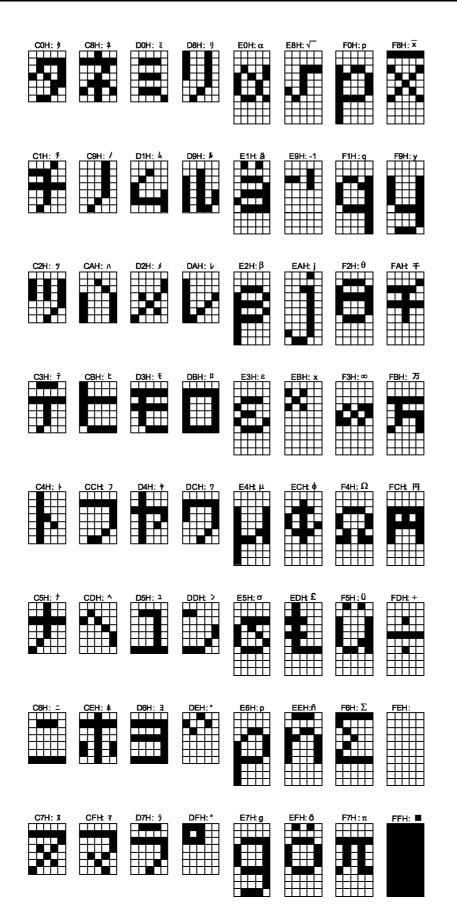

#### **Character Generator ROM (CGROM)**

The CGROM generates small character patterns ( $5 \times 7$  dots, 160 patterns) or large character patterns ( $5 \times 10$  dots, 32 patterns) from the 8-bit character code signals in the DDRAM.

When the 8-bit character code corresponding to a character pattern in the CGROM is written in the DDRAM, the character pattern is displayed in the display position specified by the DDRAM address.

Character codes 20 to 7F and A0 to FF are contained in the character code area in the CG ROM.

Character codes 20 to 7F and A0 to DF are contained in the character code area for the  $5 \times 7$ -dot character patterns. Character codes E0 to FF are contained in the ROM area for  $5 \times 10$ -dot character patterns.

The general character generator ROM codes are 01A/01B.

The relationship between character codes and general purpose character patterns are indicated in Table 2.

#### Character Generator RAM (CGRAM)

The CGRAM is used to generate user-specific character patterns that are not in the CGROM. CGRAM (64 bytes = 512 bits) can store up to 8 small character patterns ( $5 \times 8$  dots) or up to 4 large character patterns ( $5 \times 11$  dots). When displaying a character pattern stored in the CGRAM, write an 8-bit character code (00 to 07 or 08 to 0F; hex.) assigned in Table 2 to the DDRAM. This enables outputting the character pattern to the LCD display position corresponding to the DDRAM address.

The cursor or blink is also displayed even when a CGRAM or ABRAM address is set in the ADC. Therefore, the cursor or blink display should be inhibited while the ADC is holding a CGRAM or ABRAM address. The following describes how character patterns are written in and read from the CGRAM.

- 1) Small character patterns  $(5 \times 8 \text{ dots})$  (See Table 3-1.)

- (1) A method of writing character patterns to the CGRAM from the CPU

The three CGRAM address bit weights 0 to 2 select one of the lines constituting a character pattern. First, set the mode to increment or decrement from the CPU, and then input the CGRAM address. Write each line of the character pattern in the CGRAM through  $DB_0$  to  $DB_7$ .

The data lines  $DB_0$  to  $DB_7$  correspond to the CGRAM data bit weights 0 to 7, respectively (see Table 3-1). Input data "1" represents the ON status of an LCD dot and "0" represents the OFF status. Since the ADC is automatically incremented or decremented by 1 after the data is written to the CGRAM, it is not necessary to set the CGRAM address again.

The bottom line of a character pattern (the CGRAM address bit weights 0 to 2 are all "1", which means 7 in hexadecimal) is the cursor line. The ON/OFF pattern of this line is ORed with the cursor pattern for displaying on the LCD. Therefore, the pattern data for the cursor position should be all zeros to display the cursor.

Whereas the data given by the CGRAM data bit weights 0 to 4 is output to the LCD as display data, the data given by the CGRAM data bit weights 5 to 7 is not. Therefore, the CGRAM data bit weights 5 to 7 can be used as a RAM area.

(2) A method of displaying CGRAM character patterns on the LCD

The CGRAM is selected when the higher-order 4 bits of a character code are all zeros. Since bit weight 3 of a character code is not used, the character pattern "0" in Table 3-1 can be selected using the character code "00" or "08" in hexadecimal.

When the 8-bit character code corresponding to a character pattern in the CGRAM is written to the DDRAM, the character pattern is displayed in the display position specified by the DDRAM address. (The DDRAM data bit weights 0 to 2 correspond to the CGRAM address bit weights 3 to 5, respectively.)

#### 2) Large character patterns $(5 \times 11 \text{ dots})$ (See Table 3-2.)

(1) A method of writing character patterns to the CGRAM from the CPU

The four CGRAM address bit weights 0 to 3 select one of the lines constituting a character pattern. First, set the mode to increment or decrement from the CPU, and then input the CGRAM address. Write each line of the character pattern code in the CGRAM through  $DB_0$  to  $DB_7$ .

The data lines  $DB_0$  to  $DB_7$  correspond to the CGRAM data bit weights 0 to 7, respectively (see Table 3-2). Input data "1" represents the ON status of an LCD dot and "0" represents the OFF status. Since the ADC is automatically incremented or decremented by 1 after the data is written to the CGRAM, it is not necessary to set the CGRAM address again.

The bottom line of a character pattern (the CGRAM address bit weights 0 to 3 are all "1", which means A in hexadecimal) is a cursor line. The ON/OFF pattern of this line is ORed with the cursor pattern for displaying on the LCD. Therefore, the pattern data for the cursor position should be all zeros to display the cursor.

Whereas CGRAM data bit weights 0 to 4 are output as display data to the LCD when CGRAM address bit weights 0 to 3 are "0" to "A" in hexadecimal, the data given by the CGRAM data bit weights 5 to 7 or the CGRAM addresses B to F in hexadecimal is not. These bits can be written and read as a RAM area.

(2) A method of displaying CGRAM character patterns on the LCD The CCP AM is calculated when the higher order 4 bits of a character code

The CGRAM is selected when the higher-order 4 bits of a character code are all zeros. Since bit weights 0 and 3 of a character code are not used, the character pattern "g" in Table 3-2 can be selected with a character code "02", "03", "0A" or "0B" in hexadecimal.

When the 8-bit character code corresponding to a character pattern in the CGRAM is written to the DDRAM, the character pattern is displayed in the display position specified by the DDRAM address. (The DDRAM data bit weights 1 and 2 correspond to the CGRAM address bit weights 4 and 5, respectively.)

5XSn+5

E0

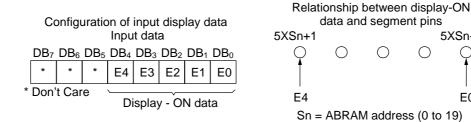

#### Arbitrator RAM (ABRAM)

The arbitrator RAM (ABRAM) stores arbitrator display data.

100 dots can be displayed in both 1-line and 2-line display modes. The arbitrator RAM has the addresses (hexadecimal) from "00" to "1F" and the valid display address area is from 00 to 19 (0H to 13H). The area of 20 to 31 (14H to 1FH) not used for display can be used as a data RAM area for general data. Even if the display is shifted by instruction, the arbitrator display is not shifted.

A capacity of 8 bits by 32 addresses (= 256 bits) is available for data write.

First set the mode to increment or decrement from the CPU, and then input the ABRAM address.

Write Display-ON data in the ABRAM through DB<sub>0</sub> to DB<sub>7</sub>.

DB<sub>0</sub> to DB<sub>7</sub> correspond to the ABRAM data bit weights 0 to 7 respectively. Input data "1" represents the ON status of an LCD dot and "0" represents the OFF status.

Since ADC is automatically incremented or decremented by 1 after the data is written to the ABRAM, it is not necessary to set the ABRAM address again.

Whereas ABRAM data bit weights 0 to 4 are output as display data to the LCD, the ABRAM data bit weights 5 to 7 are not. These bits can be used as a RAM area.

The cursor or blink is also displayed even when a CGRAM or ABRAM address is set in the ADC. Therefore, the cursor or blink display should be inhibited while the ADC is holding a CGRAM or ABRAM address.

The arbitrator RAM can store a maximum of 100 dots of the arbitrator Display-ON data in units of 5 dots. The relationship with the LCD display positions is shown below.

### Table 2 Relationship between Character Codes and Character Patterns of the ML9041A-01A/01B (General Character Codes)

The character code area in the CG ROM: Character codes 20H to 7FH, A0H to FFH.

5×7-dot ROM area: 20H to 7FH, A0H to DFH

5×10-dot ROM area: E0H to FFH The CG RAM area : Character codes 00H to 0FH 00H: 08H: 20H 28H 30H· ( 38H· 8 48H: H 50H: P CG RAM(1) CG RAM(1) 01H: 09H: 21H· 49H∙ 20H CG RAM(2) CG RAM(2) 0AH: 02H: 22H: ' CG RAM(3) CG RAM(3) 03H: 0BH: 23H: # CG RAM(4) CG RAM(4) 04H: 0CH: 24H: \$ 54H: T CG RAM(5) CG RAM(5) 05H: 0DH: 45H · F 25H  $\square$ CG RAM(6) CG RAM(6) 06H: 0EH CG RAM(7) CG RAM(7) 07H: 0FH: . ri CG RAM(8) CG RAM(8)

| CG F<br>addr |                                                                                                                                     | CG RA<br>(Charac |                                               |                                                    | DD RAM data<br>(Character code) |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------|----------------------------------------------------|---------------------------------|

| 5 4 3<br>MSB | 2 1 0                                                                                                                               | 7 6 5 4<br>MSB   |                                               |                                                    | 7 6 5 4 3 2 1 0<br>MSB LSE      |

| 000          | $\begin{array}{c} 0 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ 1 & 1 & 1 \end{array}$              |                  |                                               | 10<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>00 | 0000×000                        |

| 0 0 1        | $\begin{array}{c} 0 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ 1 & 1 & 1 \end{array}$ |                  | 0 0<br>0 1<br>1 0<br>0 1<br>0 0<br>0 0<br>0 0 | 01<br>10<br>00<br>00<br>10<br>01<br>01<br>00       | 0000×001                        |

|              |                                                                                                                                     |                  |                                               |                                                    |                                 |

|              | $\begin{array}{c} 0 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ 1 & 1 & 1 \end{array}$ |                  | 01                                            | 10<br>00<br>00<br>00<br>00<br>00<br>10<br>00       | 0000×111                        |

# Table 3-1Relationship between CGRAM address bits, CGRAM data bits (character pattern)<br/>and DDRAM data bits (character code) in 5 × 7 dot character mode. (Examples)

×: Don't Care

| CG RAM                                                          | CC DAM data                                                                        |                                 |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------|

| address                                                         | CG RAM data<br>(Character pattern)                                                 | DD RAM data<br>(Character code) |

| 543210                                                          | 76543210                                                                           | 76543210                        |

| MSB LSB                                                         | MŠB LŠB                                                                            | MŠB LSB                         |

| $ \begin{smallmatrix} 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 &$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                              | 0000×00×                        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$          | $\begin{array}{c c} \times \times \times & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0$ | 0000×01×                        |

|                                                                 |                                                                                    |                                 |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$           | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                              | 0000×11×                        |

# Table 3-2Relationship between CGRAM address bits, CGRAM data bits (character pattern)<br/>and DDRAM data bits (character code) in 5 × 10 dot character mode (Examples)

×: Don't Care

#### **Cursor/Blink Control Circuit**

This circuit generates the cursor and blink of the LCD.

The operation of this circuit is controlled by the program of the CPU.

The cursor/blink display is carried out in the position corresponding to the DDRAM address set in the ADC (Address Counter).

For example, when the ADC stores a value of "07" (hexadecimal), the cursor or blink is displayed as follows:

Note: The cursor or blink is also displayed even when a CGRAM or ABRAM address is set in the ADC. Therefore, the cursor or blink display should be inhibited while the ADC is holding a CGRAM or ABRAM address.

#### LCD Display Circuit (COM1 to COM17, SEG1 to SEG100, SSR and CSR)

The ML9041A has 17 common signal outputs and 100 segment signal outputs to display 20 characters (in the 1-line display mode) or 40 characters (in the 2-line display mode).

The character pattern is converted into serial data and transferred in series through the shift register.

The transfer direction of serial data is determined by the SSR pin. The shift direction of common signals is determined by the CSR pin. The following tables show the transfer and shift directions:

| SSR |      | Tra    | -                                      |                         |

|-----|------|--------|----------------------------------------|-------------------------|

| L   |      | SE     | _                                      |                         |

| Н   |      | SE     | $G_{100} \rightarrow SEG_1$            | _                       |

| CSR | duty | AS bit | Shift Direction                        | Arbitrator's common pin |

| L   | 1/9  | L      | $\text{COM1} \rightarrow \text{COM9}$  | COM9                    |

| L   | 1/9  | н      | $\text{COM1} \rightarrow \text{COM9}$  | COM1                    |

| L   | 1/12 | L      | $\text{COM1} \rightarrow \text{COM12}$ | COM12                   |

| L   | 1/12 | Н      | $\text{COM1} \rightarrow \text{COM12}$ | COM1                    |

| L   | 1/17 | L      | $COM1 \rightarrow COM17$               | COM17                   |

| L   | 1/17 | Н      | $\text{COM1} \rightarrow \text{COM17}$ | COM1                    |

| Н   | 1/9  | L      | $COM9 \rightarrow COM1$                | COM1                    |

| Н   | 1/9  | н      | $COM9 \rightarrow COM1$                | COM9                    |

| Н   | 1/12 | L      | $COM12 \rightarrow COM1$               | COM1                    |

| Н   | 1/12 | Н      | $COM12 \rightarrow COM1$               | COM12                   |

| Н   | 1/17 | L      | $COM17 \rightarrow COM1$               | COM1                    |

| Н   | 1/17 | Н      | $COM17 \rightarrow COM1$               | COM17                   |

\* Refer to the Expansion Instruction Codes section about the AS bit.

Signals to be input to the SSR and CSR pins should be determined at power-on and be kept unchanged.

#### **Built-in Reset Circuit**

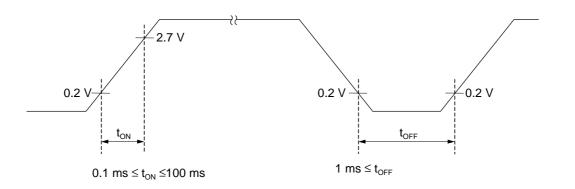

The ML9041A is automatically initialized when the power is turned on.

During initialization, the Busy Flag (BF) is "1" and the ML9041A does not accept any instruction from the CPU (other than the Read BF instruction).

The Busy Flag is "1" for about 15 ms after the  $V_{DD}$  becomes 2.7 V or higher. During this initialization, the ML9041A performs the following instructions:

| 1)  | Display clearing                               |             |

|-----|------------------------------------------------|-------------|

| 2)  | CPU interface data length $= 8$ bits           | (DL = "1")  |

| 3)  | 1-line LCD display                             | (N = "0")   |

| 4)  | Font size = $5 \times 7$ dots                  | (F = "0")   |

| 5)  | ADC counting = Increment                       | (I/D = "1") |

| 6)  | Display shifting = None                        | (S = "0")   |

| 7)  | Display = Off                                  | (D = "0")   |

| 8)  | Cursor = Off                                   | (C = "0")   |

| 9)  | Blinking = Off                                 | (B = "0")   |

| 10) | Arbitrator = Displayed in the lower line       | (AS = "0")  |